Semiconductor / Electronics Cleanrooms

In semiconductor fabrication and high-end electronics assembly, contamination is measured in parts per billion and microns. The electronics industry battles two “silent killers”: Electrostatic Discharge (ESD) Ve Ionic Contamination.

In an environment where a single microscopic particle or a stray volt can render a multi-thousand-dollar wafer useless, mop selection becomes a critical engineering decision. This guide explains how mop design impacts yield and reliability in ISO Class 3–7 environments.

In electronics manufacturing, the mechanical action of mopping creates friction, which can generate triboelectric charges. In a low-humidity cleanroom, these charges can build up on surfaces or the operator, leading to a sudden ESD event.

Standard cleaning tools often act as insulators. When an insulator is rubbed against a cleanroom floor, it creates static that cannot be bled off to the ground. This static attracts airborne particles (“magnet effect”) and risks discharging into sensitive components.

For facilities operating under strict ESD protocols, mops should be selected as part of the site’s ESD Control Program: dissipative handles, low-charging heads, and repeatable procedures. This aligns with environments typically mapped to Class 100 / 1000.

Ionic contaminants—such as sodium, potassium, chloride, and sulfate—can drive leakage, corrosion, and long-term reliability drift. In advanced nodes, “clean” must also mean ionically clean.

A mop may be low-linting but still heavily contaminated with ions from its manufacturing process. If the mop material was processed with hard water or contains chemical binders, ions can be deposited during mopping and later become airborne or tracked into critical process zones.

High-performance ISO cleanroom mops may undergo controlled laundering using high-purity DI water to reduce ionic residues and surfactants, followed by clean drying and vacuum sealing.

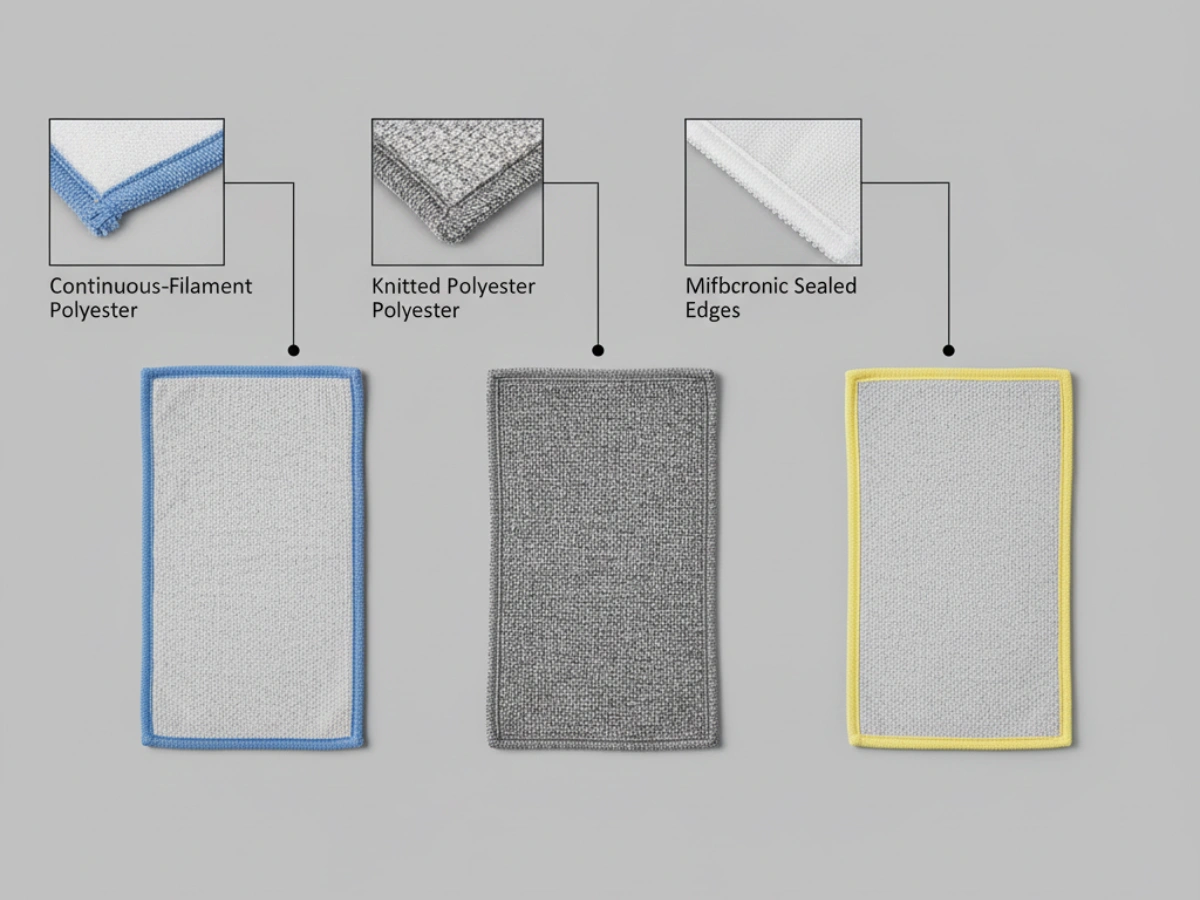

The stringency of the environment dictates the construction of the mop head. Semiconductor zones require materials that exhibit ultra-low shedding and sealed edges to prevent fiber release into airflow.

| ISO Sınıfı | Equivalent | Preferred Mop Construction |

|---|---|---|

| ISO 3–4 | Class 1–10 | 100% continuous-filament polyester, laundered, ultrasonic edges |

| ISO 5–6 | Class 100–1000 | Knitted polyester or high-density microfiber |

| ISO7 | Class 10,000 | Poly-cellulose non-woven or microfiber blends |

For the most sensitive zones, ultrasonic or laser-sealed edges help reduce loose fibers. For broader mapping across standards, see our Cleanroom Mop Selection Guide.

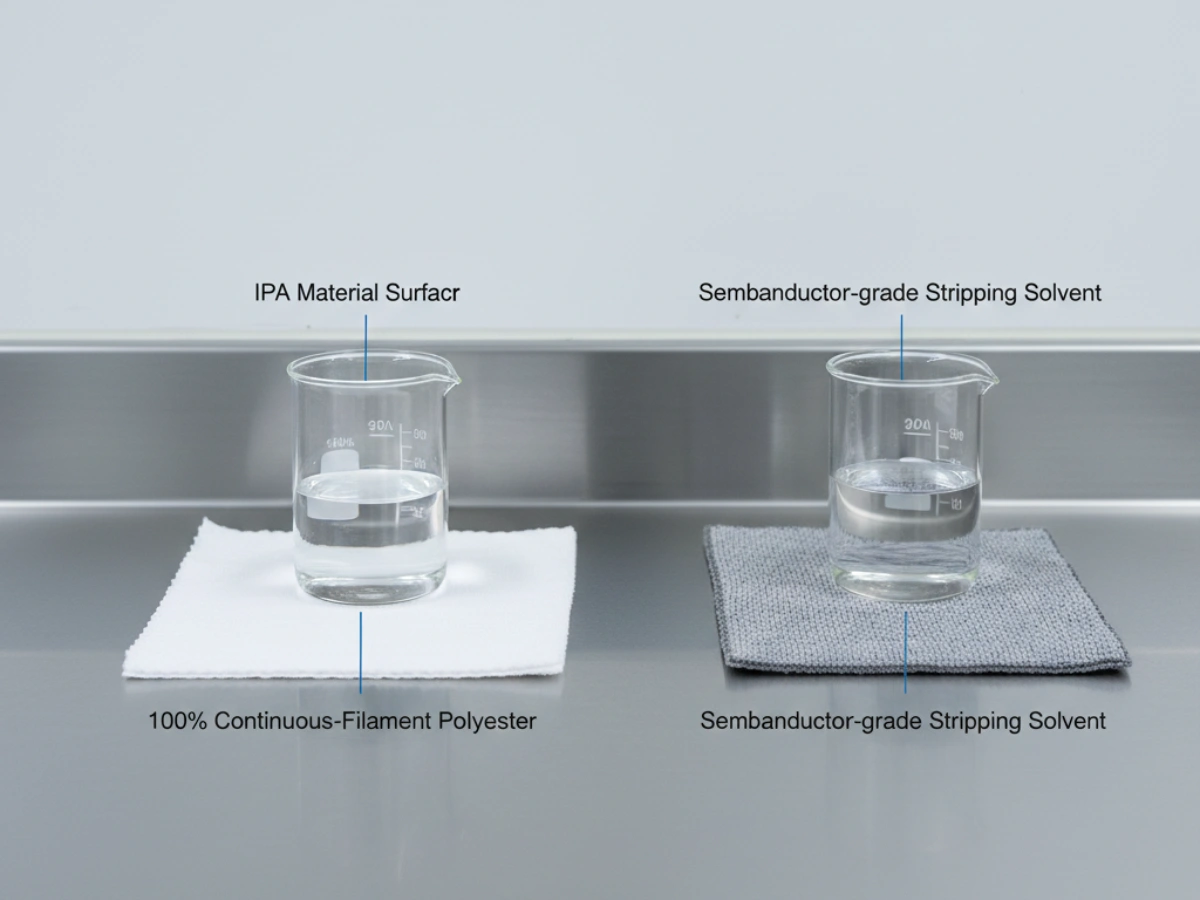

Semiconductor cleanrooms use high-purity IPA and specialized agents. Mop heads must remain chemically inert to avoid breaking down during use—and to minimize non-volatile residues (NVR).

Contamination control in electronics is a holistic discipline. Mop selection should be documented in SOPs and reviewed during yield loss investigations—especially when ESD, ionics, or particulate excursions correlate with floor control.

For cross-industry selection logic, refer to our Cleanroom Mop Selection Guide.

In semiconductor environments, “clean” is defined by molecular and electrical stability. By selecting mops that address ESD risks, ionic extractables, and particulate shedding—supported by controlled laundering and packaging—facilities reduce the silent killers that threaten production yields.

1 iş günü içinde sizinle iletişime geçeceğiz, lütfen son eki olan e-postaya dikkat edin. “*@midposi.com”.